Advanced airces, inc.

Advanced airces, inc.

Application of the policy of the policy

הההההההההההההההההההה תתתתתתתתתתתתתתתתתת תתתתתתתתתתתתתתתתתתתתת תתתתתתתתתתתתתתתתתתתתת תההההההההההההההההההההה הההההההההההההההההההההה ההההההההההההההההההההההה ההההההההההההה<u>הההההההה</u> תתתתתתתתתתתתתתתתתתתתתת תתתתתתתתתתתתתתתתתתתתתתת **הההההההההההההההההההההה** תתתתתתתתתתתתתתתתתתתתתת תתתתתתתתתתתתתתתתתתת <u> ההההההההההההההההההההה</u> תההההההההההההההההההההה תתתתתתתתתתתתתתתתתתתתתת תתתתתתתתתתתתתתתתתתתתתת**ת**

# Advanced Micro Devices MOS/LSI Data Book

#### INTRODUCTION

The first metal-oxide semiconductor (MOS), large-scale integrated (LSI) circuits were introduced in the mid-sixties. Since then, the density of MOS/LSI components has doubled every year. At the same time the cost per function has declined even faster. These developments have had a profound effect upon every aspect of electronics design and application.

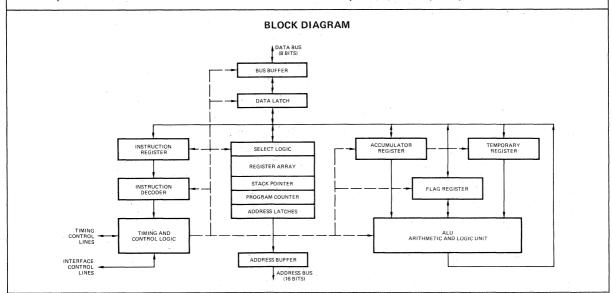

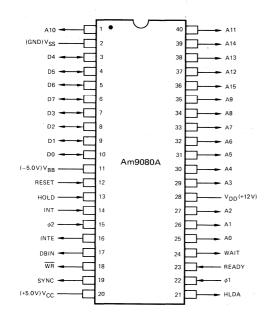

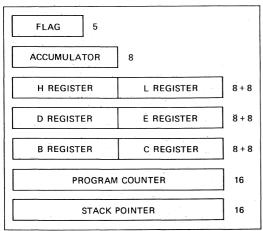

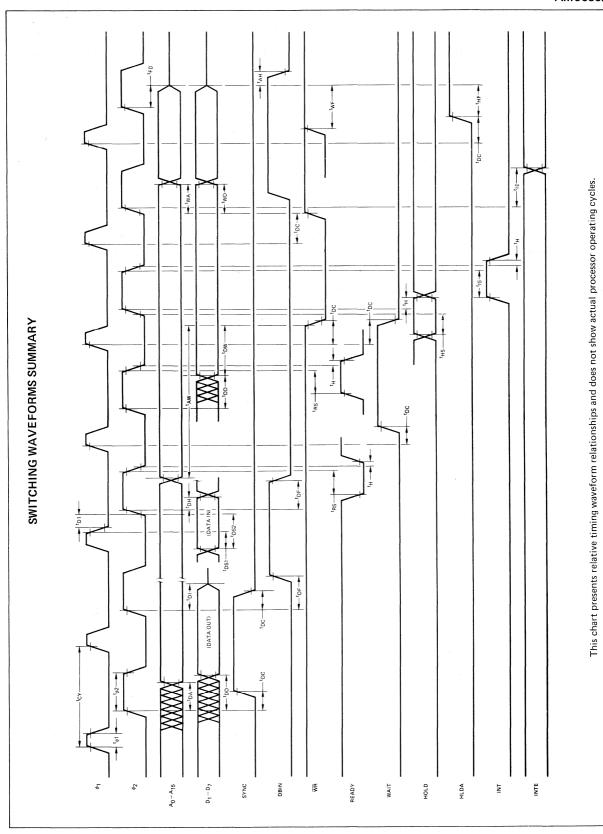

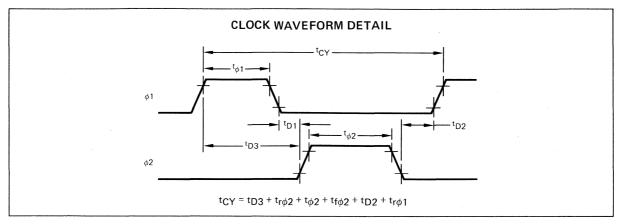

Of all the devices that have been developed to utilize the high-density, low-power characteristics of MOS/LSI, none have had as great an impact as microprocessors and memories — two areas in which Advanced Micro Devices occupies a prominent position. Microprocessors have literally revolutionized digital design by making feasible the replacement of large numbers of components with standard, relatively inexpensive microprocessor elements. The Am9080A is a pin and function compatible replacement for the industry standard 8-bit MOS microprocessor. It has electrical and timing specifications superior to those of any of its competitors. Supported by a full range of peripheral support circuits, this part has established price and technological leadership in the market.

The tremendous benefits offered by MOS memories in the storage of digital information have resulted in the huge growth of the semiconductor memory market, which is dominated by MOS/LSI devices. The earlier 1k (1024-bit) devices began to give way to 4k (4096-bit) devices during 1975. These are now in reliable, high-volume production with the problems experienced by early manufacturers/users solved. Now, people are already beginning to look forward to the 16k part, widely expected to be available in the second half of 1976.

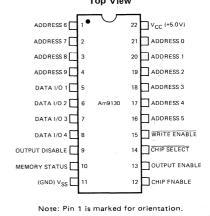

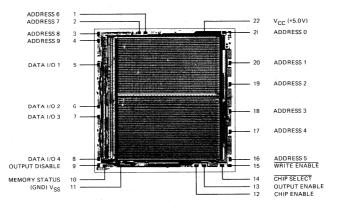

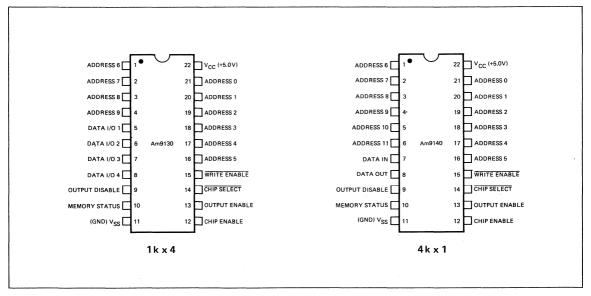

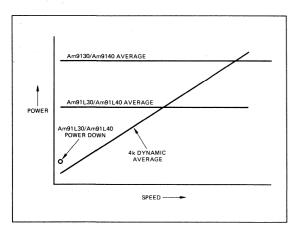

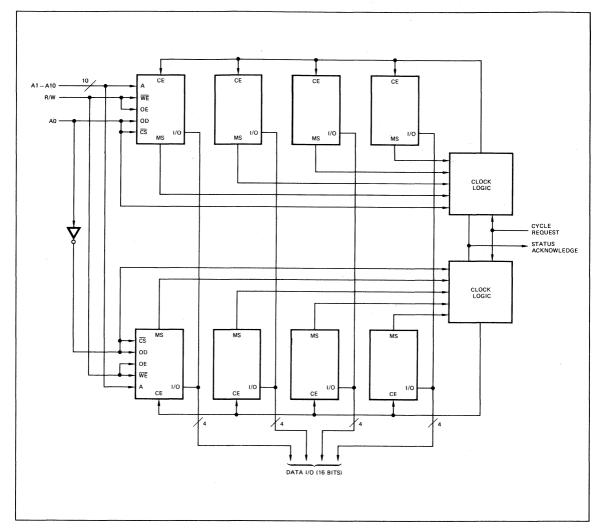

Along with the steady increase in the number of bits in a package, improvements are being made in the existing memories. Performance, power consumption and cost are all being improved. Nowhere is this more evident than in the case of the Am9130/40, 4k static RAM family, described in this data book. These parts make available the convenience of static memories (no refresh timing and control circuitry) with performance equal to or better than the best 1k static and 4k dynamic RAMs available.

The key product areas of microprocessors and memories are supported by the wide range of MOS/LSI products also described in this data book.

Copyright © 1976 by Advanced Micro Devices, Inc. 901 Thompson Place, Sunnyvale, California 94086 (408) 732-2400 TWX: 910-339-9280 TELEX: 34-6306

#### **CONTENTS**

| ı.    | GENERAL INFORMATION                  |

|-------|--------------------------------------|

|       | 1. Numerical Index                   |

|       | 2. Functional Index                  |

|       | 3. Selection Guides                  |

|       | 4. Cross Reference                   |

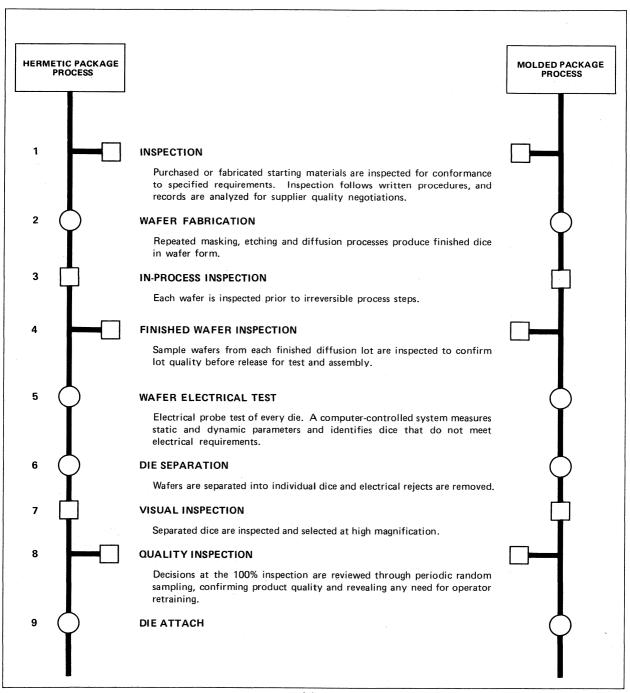

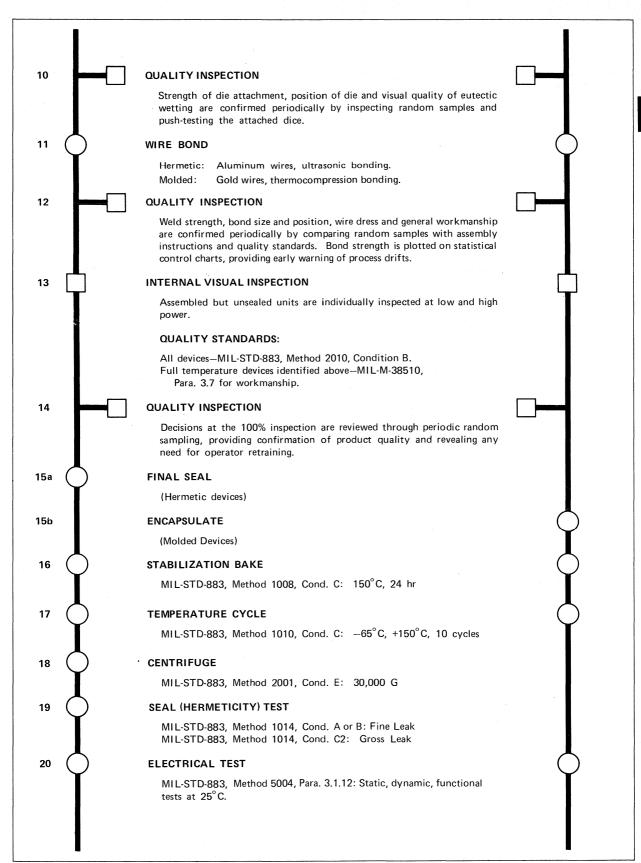

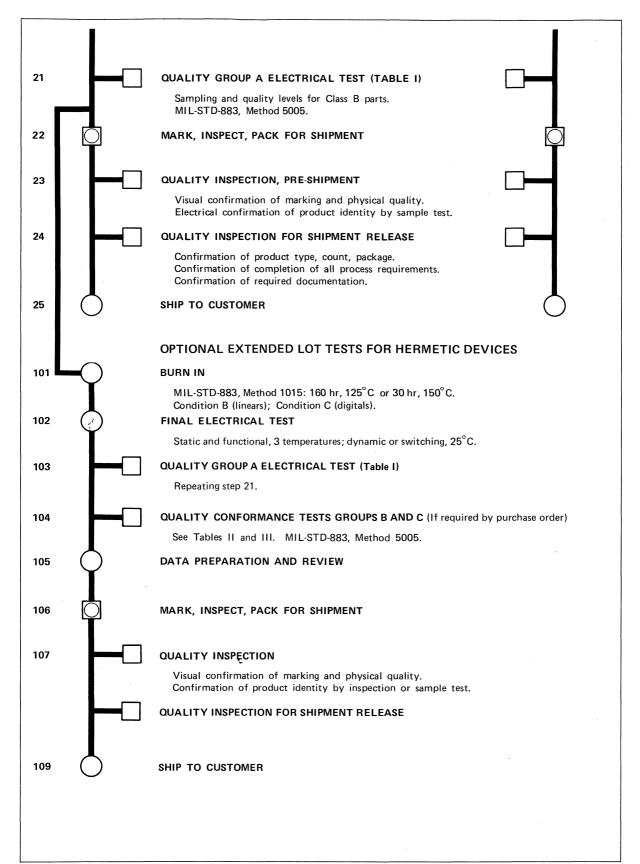

|       | 5. Process Flow                      |

| 11.   | MICROPROCESSORS & SUPPORT CIRCUITS   |

|       | 1. Numerical Index                   |

|       | 2. Selection Guide                   |

|       | 3. Data Sheets                       |

| Ш.    | RANDOM ACCESS MEMORIES (RAM's)       |

|       | 1. Numerical Index                   |

|       | 2. Selection Guide                   |

|       | 3. Data Sheets                       |

| IV.   | READ ONLY MEMORIES (ROM's, EROM's)   |

|       | 1. Numerical Index                   |

|       | 2. Selection Guide                   |

|       | 3. Data Sheets                       |

| V.    | SHIFT REGISTERS                      |

|       | 1. Numerical Index                   |

|       | 2. Selection Guide                   |

|       | 3. Data Sheets                       |

| VI.   | FIRST-IN FIRST-OUT MEMORIES (FIFO's) |

|       | 1. Numerical Index                   |

|       | 2. Selection Guide                   |

|       | 3. Data Sheets                       |

| VII.  | APPLICATION NOTES                    |

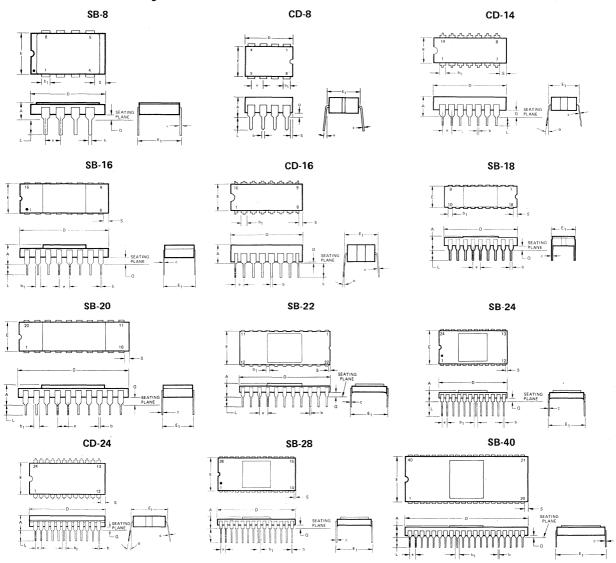

| VIII. | PACKAGE INFORMATION                  |

|       |                                      |

| IX.   | SALES OFFICES                        |

#### **NUMERICAL INDEX**

| Product           | Description                                                                                         |

|-------------------|-----------------------------------------------------------------------------------------------------|

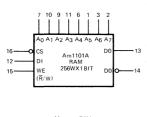

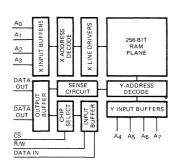

| Am1101A           | 256-Bit Static RAM                                                                                  |

| Am1101A1          | 256-Bit Static RAM                                                                                  |

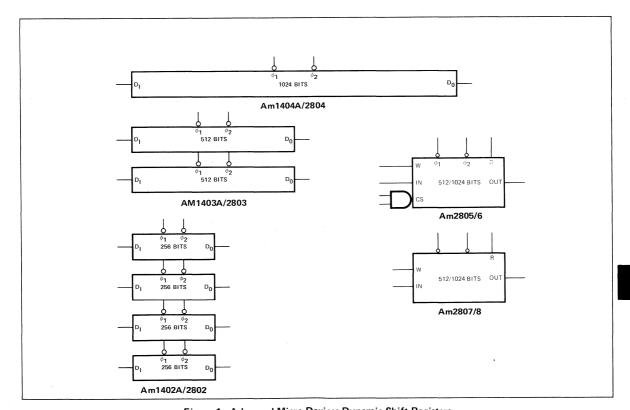

| Am1402A           | Quad 256-Bit Dynamic S/R                                                                            |

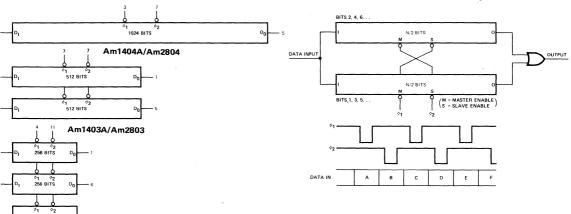

| Am1403A           | Dual 512-Bit Dynamic S/R                                                                            |

| Am1404A           | Single 1024-Bit Dynamic S/R                                                                         |

| Am1405A           | 512-Bit Dynamic Recirculate S/R                                                                     |

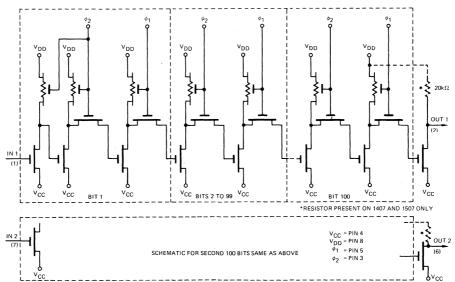

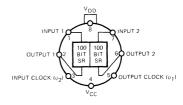

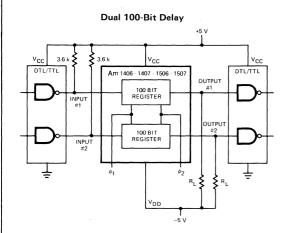

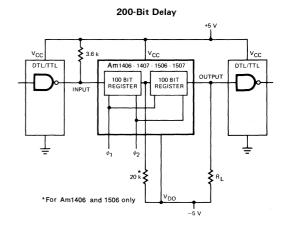

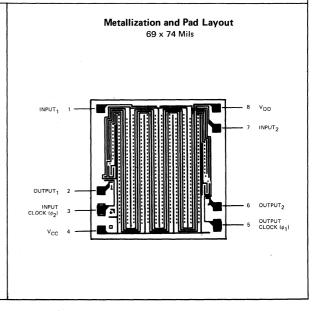

| Am1406/1506       | Dual 100-Bit Dynamic S/R                                                                            |

| Am1407/1507       | Dual 100-Bit Dynamic S/R (20k pull down)                                                            |

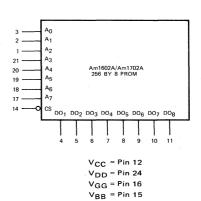

| Am1702A           | 256 x 8 Ultraviolet Erasable ROM                                                                    |

| Am2101 (see 9101) | 256 x 4-Bit Static RAM Family (22 Pin)                                                              |

| Am2102 (see 9102) | 1024 x 1-Bit Static RAM Family (16 Pin)                                                             |

| Am2111 (see 9111) | 256 x 4-Bit Static RAM Family (18 Pin)                                                              |

| Am2112 (see 9112) | 256 x 4-Bit Static RAM Family (16 Pin)                                                              |

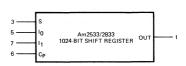

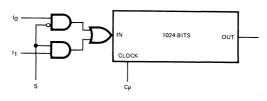

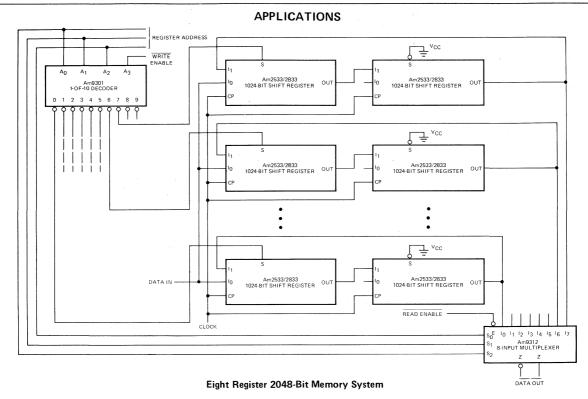

| Am2533 (see 2833) | 1024-Bit Static S/R                                                                                 |

| *Am25LS138        | 1-of-8 Binary Decoder                                                                               |

| *Am25LS/139       | Dual 1-of-4 Decoder                                                                                 |

| Am2802            | O LOSC D: D O/D /404411 \                                                                           |

| Am2803            | Quad 256-Bit Dynamic S/R (10MHz)         5-9           Dual 512-Bit Dynamic S/R (10MHz)         5-9 |

| Am2804            | Single 1024-Bit Dynamic S/R (10MHz)                                                                 |

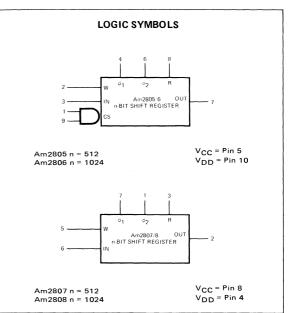

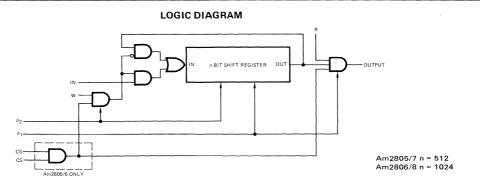

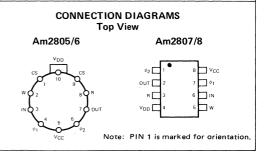

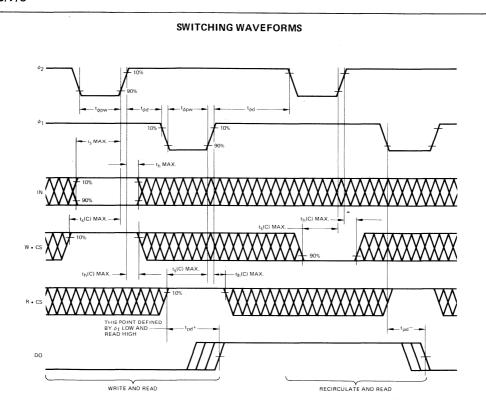

| Am2805            | 512-Bit Dynamic Recirculate S/R                                                                     |

| Am2806            | 1024-Bit Dynamic Recirculate S/R                                                                    |

| Am2807            | 512-Bit Dynamic Recirculate S/R                                                                     |

| Am2808            | 1024-Bit Dynamic Recirculate S/R                                                                    |

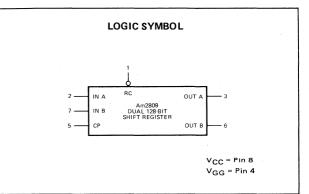

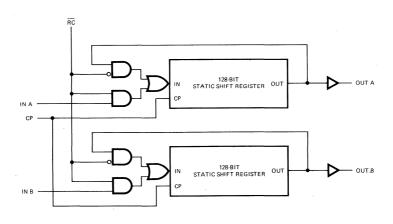

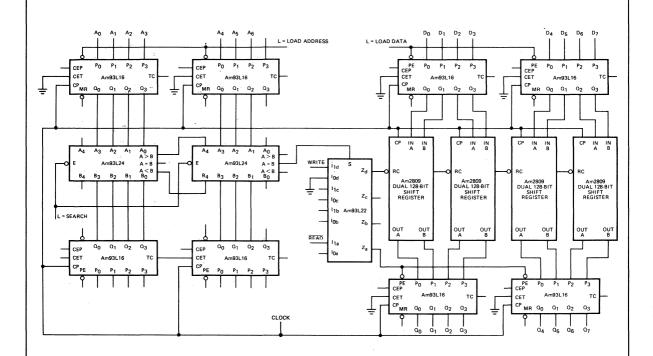

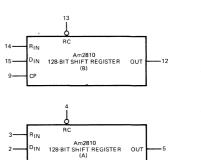

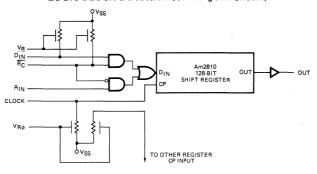

| Am2809            | Dual 128-Bit Static S/R                                                                             |

| Am2810            |                                                                                                     |

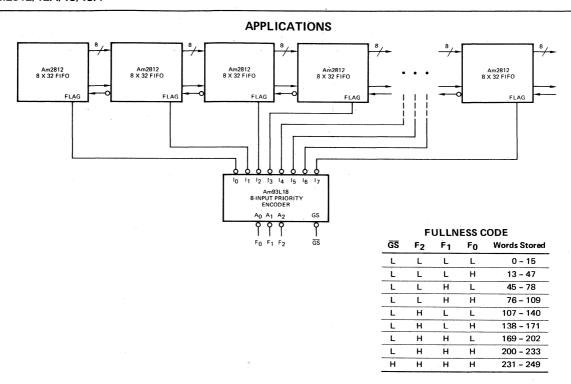

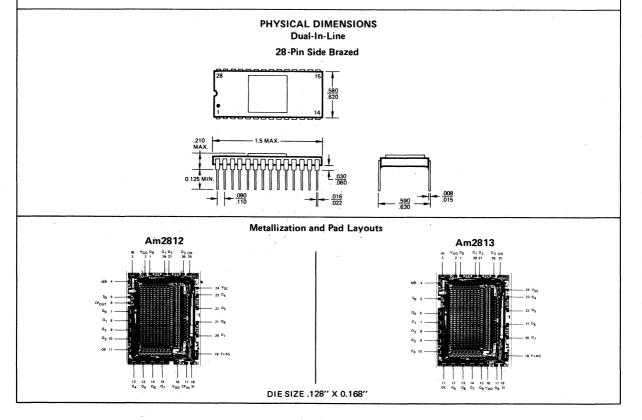

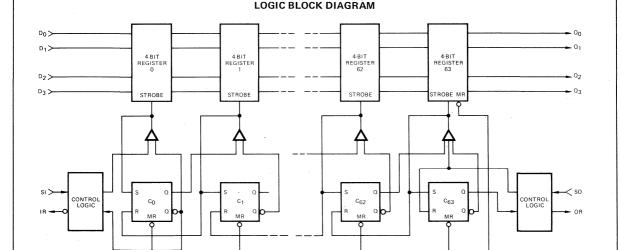

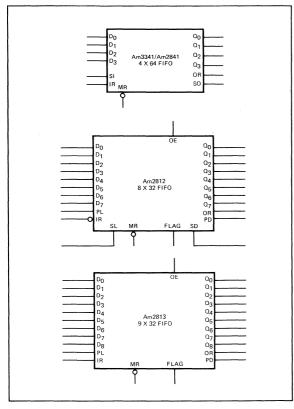

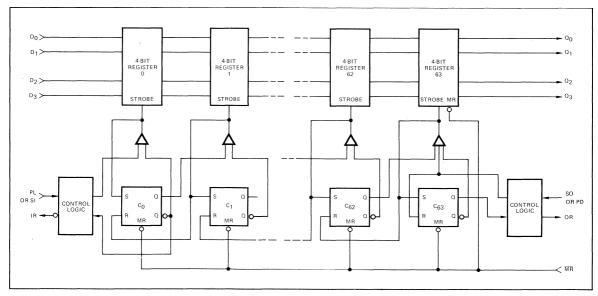

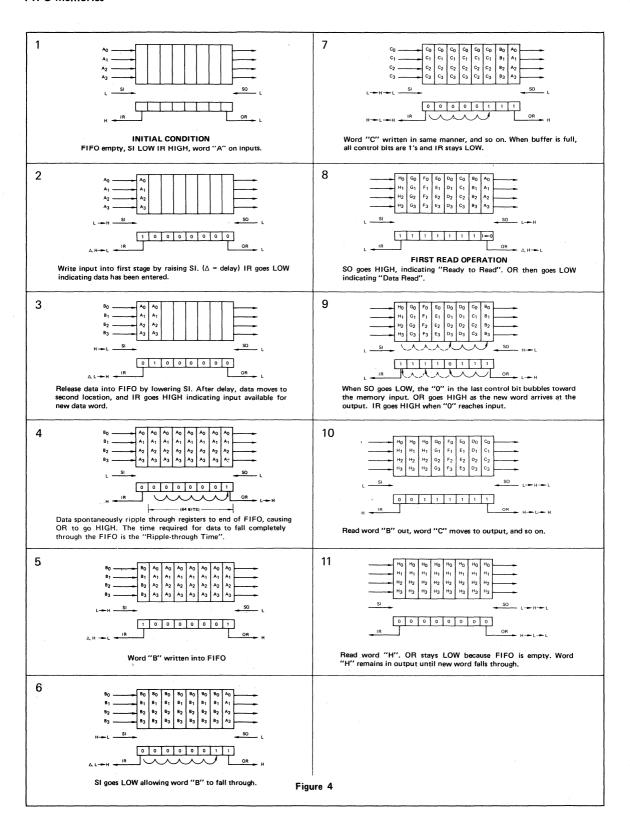

| Am2812            | Dual 128-Bit Static S/R                                                                             |

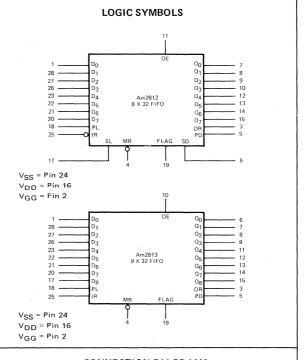

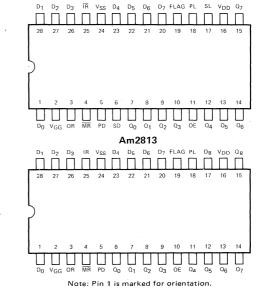

|                   | 32 x 8 FIFO Memory                                                                                  |

| Am2813            | 32 x 9 FIFO Memory                                                                                  |

| Am2814            | Dual 128-Bit Static S/R                                                                             |

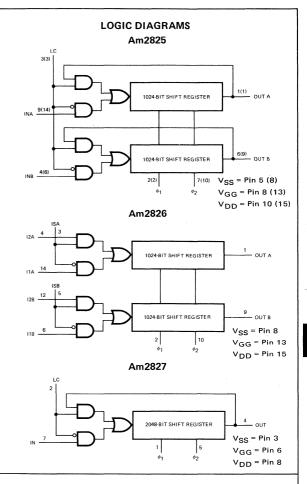

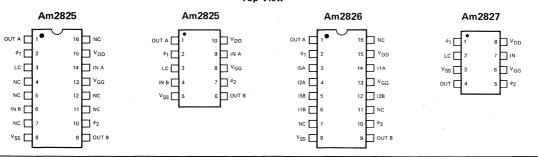

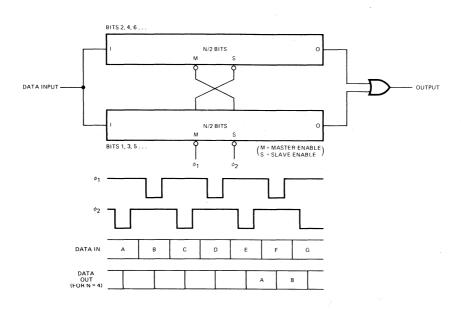

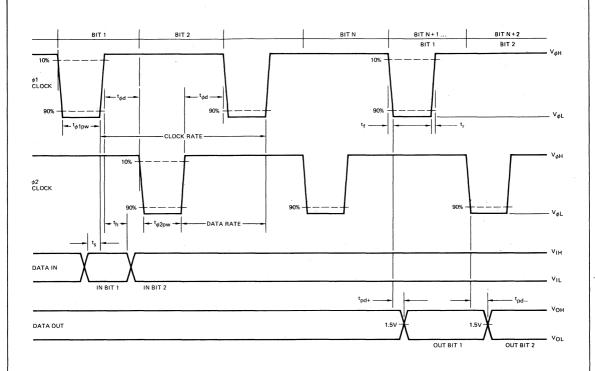

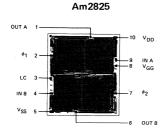

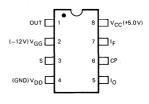

| Am2825            | Dual 1024-Bit Dynamic S/R                                                                           |

| Am2826            | Dual 1024-Bit Dynamic S/R                                                                           |

| Am2827            | 2048-Bit Dynamic S/R                                                                                |

| Am2833            | 1024-Bit Dynamic S/R (2.0MHz)                                                                       |

| Am2841            | 64 x 4 FIFO Memory                                                                                  |

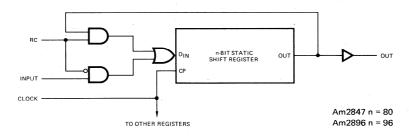

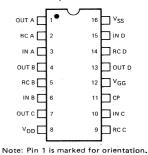

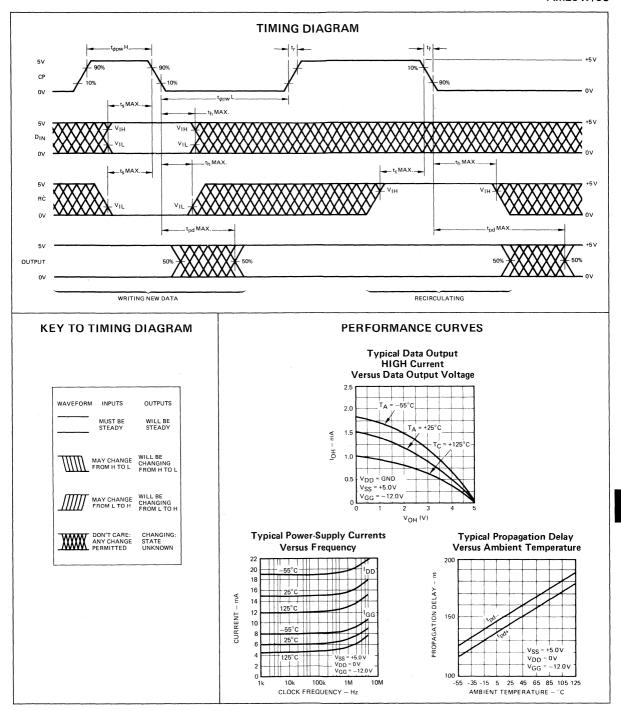

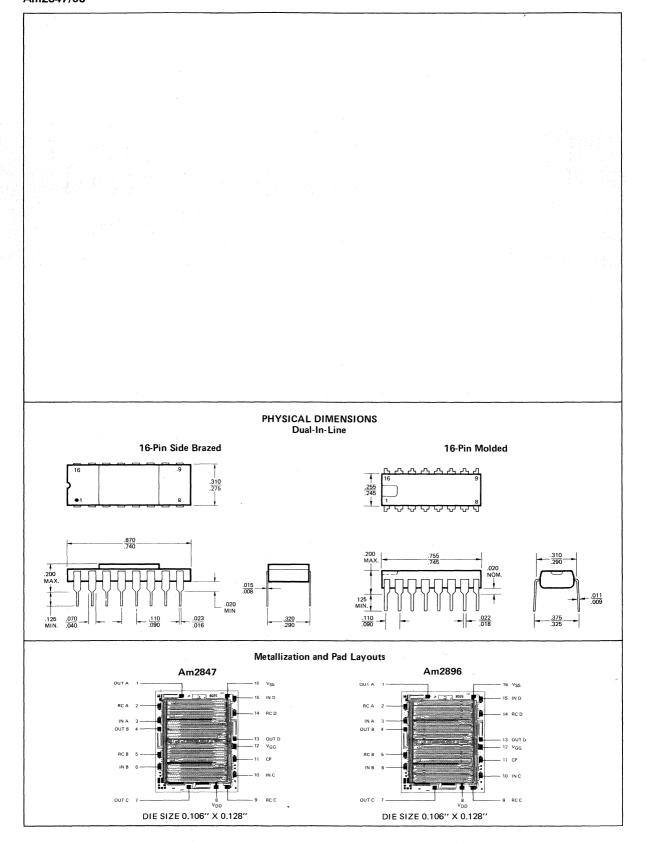

| Am2847            | Quad 80-Bit Static S/R                                                                              |

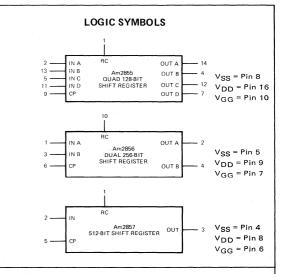

| Am2855            | Quad 128-Bit Static S/R                                                                             |

| Am2856            | Dual 256-Bit Static S/R                                                                             |

| Am2857            | Single 512-Bit Static S/R                                                                           |

| Am2896            | Quad 90-Bit Static S/R                                                                              |

| Am3341 (see 2841) | 64 x 4 FIFO Memory                                                                                  |

| Am3514 (see 9214) | 256 x 8-Bit Mask Programmable ROM                                                                   |

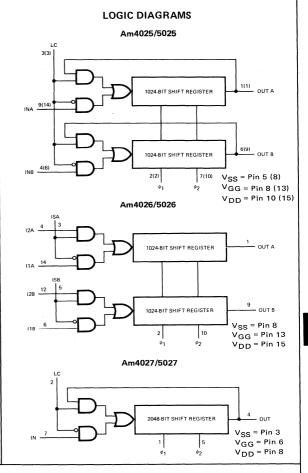

| Am4025/5025       | Dual 1024-Bit Dynamic S/R                                                                           |

| Am4026/5026       | Dual 1024-Bit Dynamic S/R                                                                           |

| Am4027/5027       | 2048-Bit Dynamic S/R                                                                                |

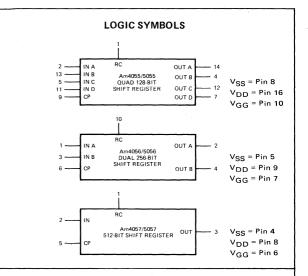

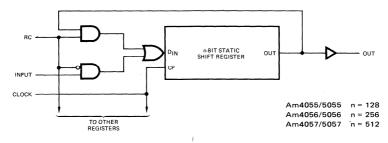

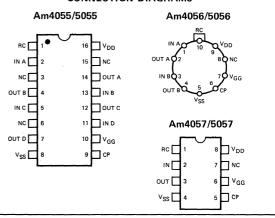

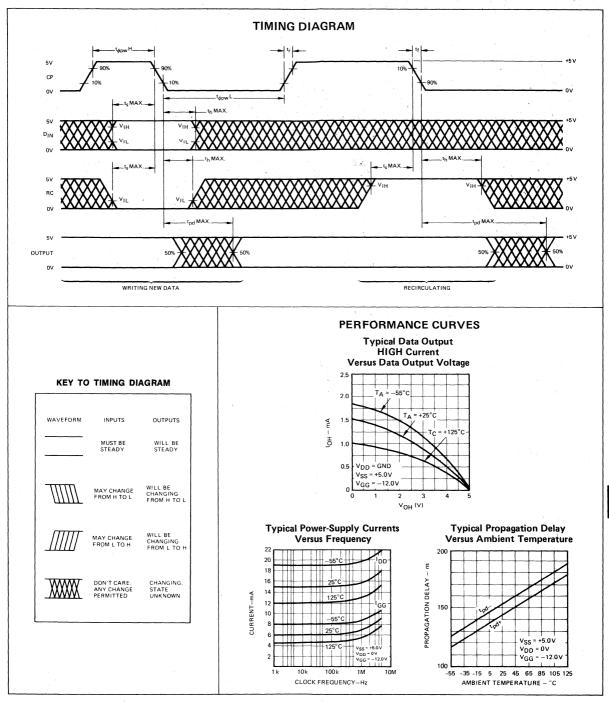

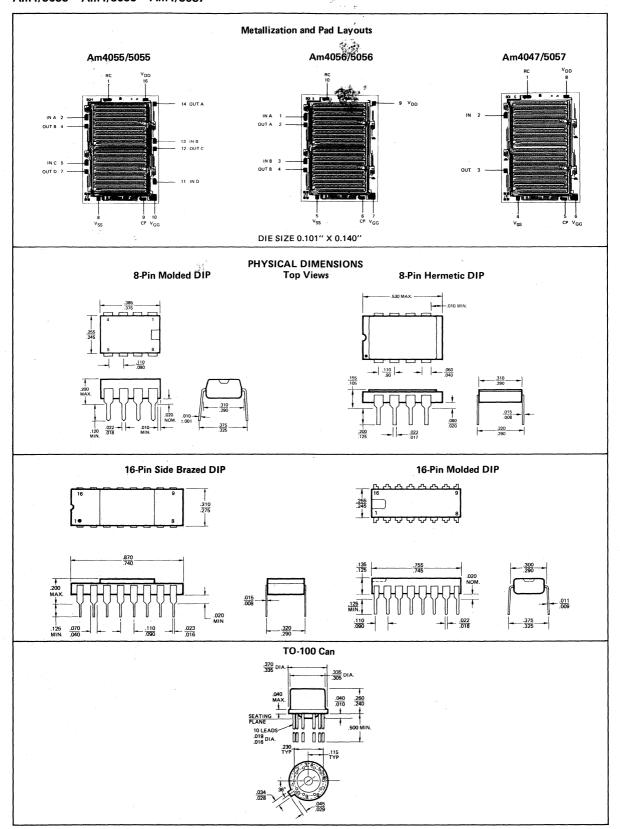

| Am4055/5055       | Quad 128-Bit Static S/R                                                                             |

| Am4056/5056       | Dual 256-Bit Static S/R                                                                             |

| Am4057/5057       | Single 512-Bit Static S/R                                                                           |

| *Am8212           | 8-Bit I/O Port                                                                                      |

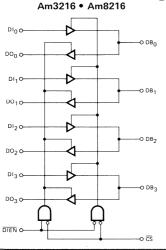

| *Am8216           | Quad Non-Inverting Bus Driver                                                                       |

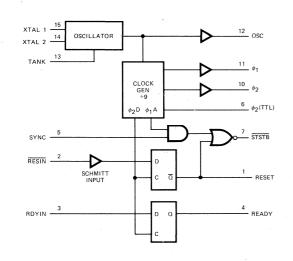

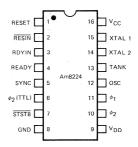

| *Am8224           | Clock Generator                                                                                     |

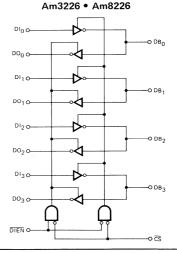

| *Am8226           | Quad Inverting Bus Driver                                                                           |

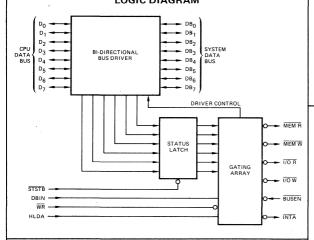

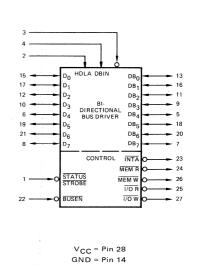

| *Am8228           | System Controller                                                                                   |

| Am9050C           | 4096 x 1 300 nsec Dynamic RAM (18 Pin)                                                              |

| Am9050D           | 4096 x 1 250 nsec Dynamic RAM (18 Pin)                                                              |

| Am9050E           | 4096 x 1 200 nsec Dynamic RAM (18 Pin)                                                              |

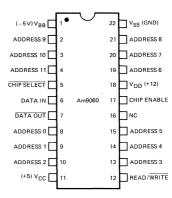

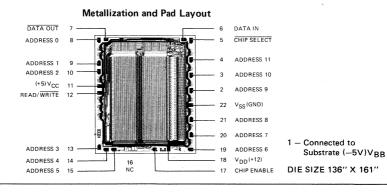

| Am9060C           | 4096 x 1 300 nsec Dynamic RAM (22 Pin)                                                              |

| Am9060D           | 4096 x 1 250 nsec Dynamic RAM (22 Pin)                                                              |

| Am9060E           | 4096 x 1 200 nsec Dynamic RAM (22 Pin)                                                              |

|                   | 3-15                                                                                                |

<sup>\*</sup>Bipolar Support Circuit for the MOS Microprocessor

#### **NUMERICAL INDEX (Cont.)**

| Product        | Description                                         | Page   |

|----------------|-----------------------------------------------------|--------|

| Am9080A        | 8-Bit Single Chip MOS Microprocessor (480 nsec)     | 2-3    |

| Am9080A-1      | 8-Bit Single Chip MOS Microprocessor (320 nsec)     | 2-3    |

| Am9080A-2      | 8-Bit Single Chip MOS Microprocessor (380 nsec)     | 2-3    |

| Am9080A-4      | 8-Bit Single Chip MOS Microprocessor (250 nsec)     |        |

| Am9101A/91L01A | 256 x 4-Bit Std./L.P.500 nsec Static RAM (22 Pin)   | . 3-21 |

| Am9101B/91L01B | 256 x 4-Bit Std./L.P. 400 nsec Static RAM (22 Pin)  | . 3-21 |

| Am9101C/91L01C | 256 x 4-Bit Std./L.P. 300 nsec Static RAM (22 Pin)  | . 3-21 |

| Am9101D        | 256 x 4-Bit 250 nsec Static RAM (22 Pin)            | . 3-21 |

| Am9101E        | 256 x 4-Bit 200 nsec Static RAM (22 Pin)            | . 3-21 |

| Am9102/91L02   | 1024 x 1-Bit Std./L.P. 650 nsec Static RAM (16 Pin) | 3-27   |

| Am9102A/91L02A | 1024 x 1-Bit Std./L.P. 500 nsec Static RAM (16 Pin) | . 3-27 |

| Am9102B/91L02B | 1024 x 1-Bit Std./L.P. 400 nsec Static RAM (16 Pin) | . 3-27 |

| Am9102C/91L02C | 1024 x 1-Bit Std./L.P.300 nsec Static RAM (16 Pin)  | 3-27   |

| Am9102D        | 1024 x 1-Bit 250 nsec Static RAM (16 Pin)           | 3-27   |

| Am9102E        | 1024 x 1-Bit 200 nsec Static RAM (16 Pin)           | 3-27   |

| Am9111A/91L11A | 256 x 4-Bit Std./L.P. 500 nsec Static RAM (18 Pin)  | 3-33   |

| Am9111B/91L11B | 256 x 4-Bit Std./L.P. 400 nsec Static RAM (18 Pin)  | 3-33   |

| Am9111C/91L11C | 256 x 4-Bit Std./L.P. 300 nsec Static RAM (18 Pin)  |        |

| Am9111D        | 256 x 4-Bit 250 nsec Static RAM (18 Pin)            | 3-33   |

| Am9111E        | 256 x 4-Bit 200 nsec Static RAM (18 Pin)            | . 3-33 |

| Am9112A/91L12A | 256 x 4-Bit Std./L.P. 500 nsec Static RAM (16 Pin)  | 3-39   |

| Am9112B/91L12B | 256 x 4-Bit Std./L.P. 400 nsec Static RAM (16 Pin)  | 3-39   |

| Am9112C/91L12C | 256 x 4-Bit Std./L.P. 300 nsec Static RAM (16 Pin)  | 3-39   |

| Am9112D        | 256 x 4-Bit 250 nsec Static RAM (16 Pin)            |        |

| Am9112E        | 256 x 4-Bit 200 nsec Static RAM (16 Pin)            | 3-39   |

| Am9130A        | 1024 x 4-Bit 500 nsec Static RAM                    | 3-45   |

| Am9130B        | 1024 x 4-Bit 400 nsec Static RAM                    | 3-45   |

| Am9130C        | 1024 x 4-Bit 300 nsec Static RAM                    | 3-45   |

| Am9130E        | 1024 x 4-Bit 200 nsec Static RAM                    | 3-45   |

| Am9140A        | 4096 x 1-Bit 500 nsec Static RAM                    |        |

| Am9140B        | 4096 x 1-Bit 400 nsec Static RAM                    | 3-49   |

| Am9140C        | 4096 x 1-Bit 300 nsec Static RAM                    | 3-49   |

| Am9140E        | 4096 x 1-Bit 200 nsec Static RAM                    | 3-49   |

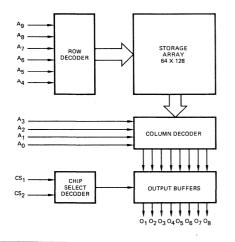

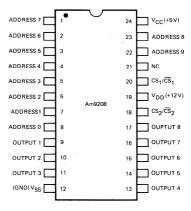

| Am9208B        | 1024 x 8-Bit 400 nsec Mask Programmable ROM         | 4-9    |

| Am9208C        | 1024 x 8-Bit 300 nsec Mask Programmable ROM         | 4-9    |

| Am9208D        | 1024 x 8-Bit 250 nsec Mask Programmable ROM         | 4-9    |

| Am9214         | 512 x 8-Bit 500 nsec Mask Programmable ROM          | 4-13   |

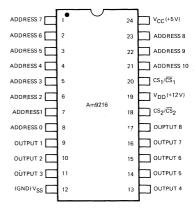

| Am9216B        | 2048 x 8-Bit 400 nsec Mask Programmable ROM         | 4-19   |

| Am9216C        | 2048 x 8-Bit 300 nsec Mask Programmable ROM         | 4-19   |

| Am9401/2401    | Dual 1024-Bit Dynamic Shift Register                | 2 17   |

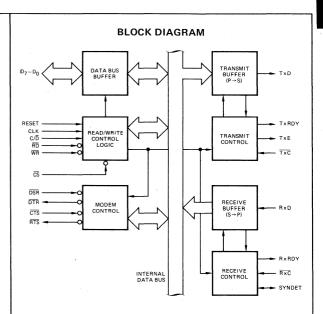

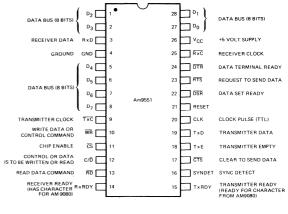

| Am9551         | Programmable Communications Interface               | 2.17   |

| Am0555         | Programmable Peripheral Interface                   | 2-18   |

#### **FUNCTIONAL INDEX**

| Static R/W Random Access Memories    |                        |        |

|--------------------------------------|------------------------|--------|

| Organization                         | Part Number            | Page   |

| 256 x 1                              | Am1101A/1101A1/1101A51 | . 3-3  |

| 256 × 4                              | Am9101/91L01/2101      | . 3-21 |

| 256 x 4                              | Am9111/91L11/2111      | . 3-33 |

|                                      | Am9112/91L12/2112      |        |

|                                      | Am9102/91L02/2102      |        |

|                                      | Am9130                 |        |

|                                      |                        |        |

| 4096 x 1                             | Am9140                 | . 3-49 |

| Dunamia D AM Davidania A acces Mamor | ion                    |        |

| Dynamic R/W Random Access Memor      |                        |        |

| Organization                         | Part Number            | Page   |

|                                      | Am9050                 |        |

| 4096 x 1                             | Am9060                 | . 3-15 |

| Erecable Bond Only Memories          |                        |        |

| Erasable Read Only Memories          | Dank Nameda            |        |

| Organization                         | Part Number            | Page   |

| 256 × 8                              | Am1702A                | . 4-4  |

| Pood Only Momories                   |                        |        |

| Read Only Memories                   | D. AN. I               | _ `    |

| Organization                         | Part Number            | Page   |

|                                      | Am9214/3514            |        |

| 1024 x 8                             | Am9208                 | . 4-9  |

| 2048 x 8                             | Am9216                 | . 4-19 |

| Demands Chiff Desistant              |                        |        |

| Dynamic Shift Registers              |                        | _      |

| Organization                         | Part Number            | Page   |

|                                      | Am1406/1506            |        |

|                                      | Am1407/1507            |        |

| 256-Bit-Quad                         | Am2802/1402A           | . 5-9  |

| 512-Bit-Single                       | Am2805/2807            | . 5-15 |

| 512-Bit-Dual                         | Am2803/1403A           | . 5-9  |

|                                      | Am2804/1404A           |        |

|                                      | Am2806/Am2808          |        |

|                                      | Am9401/2401            |        |

|                                      | Am2825                 |        |

|                                      |                        |        |

|                                      | Am4025/5025            |        |

|                                      | Am2826                 |        |

| 1024-Bit-Dual                        | Am4026/5026            | . 5-51 |

| 2048-Bit-Single                      | Am2827                 | . 5-33 |

| 2048-Bit-Single                      | Am4027/5027            | . 5-57 |

| Out the Date                         |                        |        |

| Static Shift Registers               | D. ( No. and an        | _      |

| Organization                         | Part Number            | Page   |

| 80-Bit-Quad                          |                        |        |

| 96-Bit-Quad                          | Am2896                 | . 5-43 |

| 128-Bit-Dual                         | Am2809                 | . 5-21 |

| 128-Bit-Dual                         | Am2810                 | . 5-25 |

|                                      | Am2814/3114            |        |

|                                      | Am2855                 |        |

|                                      | Am4055/5055            | -      |

|                                      | Am2856                 |        |

|                                      |                        | •      |

|                                      | Am4056/5056            |        |

|                                      | Am2857                 |        |

| 5                                    | Am4057/5057            | •      |

| 1024-Bit-Single                      | Am2833/2533            | . 5-39 |

|                                      |                        |        |

#### **FUNCTIONAL INDEX (Cont.)**

| First-In First-Out Memories          |                  |

|--------------------------------------|------------------|

| Organization                         | Part Number Page |

|                                      | . Am2812         |

|                                      | . Am2813         |

| 64 x 4-Bit                           | . Am2841/33416-9 |

| Microprocessors & Support Circuits   |                  |

| Function                             | Part Number Page |

| 8-Bit Single Chip MOS Microprocessor | . Am9080A/8080A  |

| * 1-of-8 Binary Decoder              | . Am25LS138      |

| * Dual 1-of-4 Decoder                | . Am25LS139      |

| * 8-Bit I/O Port                     | . Am8212         |

|                                      | . Am8216         |

|                                      | . Am8224         |

| * Inverting Bus Driver               | . Am8226         |

| * System Controller                  | . Am8228         |

| Programmable Communication Interface | . Am9551         |

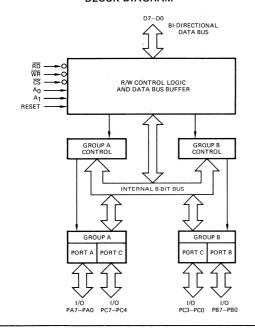

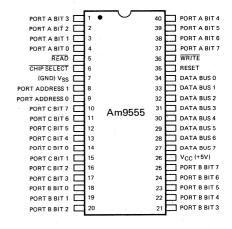

| Programmable Peripheral Interface    | Am9555           |

<sup>\*</sup> Bipolar Support Circuit for the MOS Microprocessor

#### **SELECTION GUIDES**

#### STATIC R/W RANDOM ACCESS MEMORIES

| Am9101A         256 x 4         500         C, M         +5         3-State         Separate         22         290         46           Am9101B         256 x 4         400         C, M         +5         3-State         Separate         22         290         46           Am91L01B         256 x 4         400         C, M         +5         3-State         Separate         22         290         46           Am91L01B         256 x 4         300         C, M         +5         3-State         Separate         22         173         37           Am9101C         256 x 4         300         C, M         +5         3-State         Separate         22         189         37           Am9101D         256 x 4         200         C         +5         3-State         Separate         22         315         46           Am9101E         256 x 4         200         C         +5         3-State         Separate         16         263         42           Am9102D         1024 x 1         650         C, M         +5         3-State         Separate         16         263         42           Am9102D         1024 x 1         500         C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Part<br>Number | Organiza-<br>tion | Maximum<br>Access<br>Time<br>(ns) | Temp.<br>Range | Supply<br>Voltage | Outputs | Data I/O<br>Config-<br>uration        | Package<br>Pins | Operating<br>Power<br>Max.<br>(mW) | Standby<br>Power<br>Max.<br>(mW) |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|-----------------------------------|----------------|-------------------|---------|---------------------------------------|-----------------|------------------------------------|----------------------------------|

| Am9101B         256 x 4         400         C, M         +5         3-State         Separate         22         290         46           Am91L01B         256 x 4         400         C, M         +5         3-State         Separate         22         173         37           Am91D1C         256 x 4         300         C, M         +5         3-State         Separate         22         189         37           Am9101D         256 x 4         250         C         +5         3-State         Separate         22         189         37           Am9101D         256 x 4         250         C         +5         3-State         Separate         22         315         46           Am9102         1024 x 1         650         C, M         +5         3-State         Separate         16         263         42           Am9102A         1024 x 1         650         C, M         +5         3-State         Separate         16         158         35           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Am9101A        | 256 × 4           | 500                               | C, M           | +5                | 3-State | Separate                              | 22              | 290                                | 46                               |

| Am9101B         256 x 4         400         C, M         +5         3-State         Separate         22         290         46           Am91L01B         256 x 4         400         C, M         +5         3-State         Separate         22         173         37           Am9101C         256 x 4         300         C, M         +5         3-State         Separate         22         189         37           Am9101D         256 x 4         250         C         +5         3-State         Separate         22         315         46           Am9101E         256 x 4         250         C         +5         3-State         Separate         22         315         46           Am9102         1024 x 1         660         C, M         +5         3-State         Separate         16         263         42           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Am91L01A       | 256 × 4           | 500                               |                | +5                | 3-State | Separate                              | 22              | 173                                | 37                               |

| Am91L01B         256 x 4         400         C, M         +5         3-State         Separate         22         173         37           Am91L01C         256 x 4         300         C, M         +5         3-State         Separate         22         189         37           Am9101D         256 x 4         250         C         +5         3-State         Separate         22         315         46           Am9101D         256 x 4         200         C         +5         3-State         Separate         22         315         46           Am9101D         256 x 4         200         C         +5         3-State         Separate         22         315         46           Am9102D         1024 x 1         650         C, M         +5         3-State         Separate         16         158         35           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Am9101B        | 256 × 4           | 400                               |                | +5                | 3-State |                                       | 22              | 290                                |                                  |

| Am91L01C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Am91L01B       | 256 x 4           | 400                               |                | +5                | 3-State | Separate                              | 22              | 173                                | 37                               |

| Am91L01C         256 x 4         300         C, M         +5         3-State         Separate         22         189         37           Am9101D         256 x 4         250         C         +5         3-State         Separate         22         315         46           Am9101E         256 x 4         200         C         +5         3-State         Separate         16         263         42           Am9102         1024 x 1         650         C, M         +5         3-State         Separate         16         263         42           Am91L02         1024 x 1         650         C, M         +5         3-State         Separate         16         188         35           Am91L02A         1024 x 1         500         C, M         +5         3-State         Separate         16         188         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am9102D         1024 x 1         300 <td< td=""><td>Am9101C</td><td>256 x 4</td><td>300</td><td>· ·</td><td>+5</td><td>3-State</td><td>Separate</td><td>22</td><td>315</td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Am9101C        | 256 x 4           | 300                               | · ·            | +5                | 3-State | Separate                              | 22              | 315                                |                                  |

| Am9101D         256 x 4         250         C         +5         3-State         Separate         22         315         46           Am9101E         256 x 4         200         C         +5         3-State         Separate         22         315         46           Am9102         1024 x 1         650         C, M         +5         3-State         Separate         16         263         42           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am9102E         1024 x 1         250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Am91L01C       | 256 × 4           | 300                               |                | +5                | 3-State | Separate                              | 22              |                                    |                                  |

| Am9101E         256 x 4         200         C         +5         3-State         Separate         22         315         46           Am9102         1024 x 1         650         C, M         +5         3-State         Separate         16         263         42           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         263         42           Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C, M         +5         3-State         Separate         16         173         35           Am9102D         1024 x 1         250         C         +5         3-State         Separate         16         290         42           Am9111A         256 x 4         500 <t< td=""><td>Am9101D</td><td>256 × 4</td><td>250</td><td></td><td>+5</td><td></td><td></td><td>22</td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Am9101D        | 256 × 4           | 250                               |                | +5                |         |                                       | 22              |                                    |                                  |

| Am91L02         1024 x 1         650         C, M         +5         3-State         Separate         16         158         35           Am91D2A         1024 x 1         500         C, M         +5         3-State         Separate         16         263         42           Am91L02A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         263         42           Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C, M         +5         3-State         Separate         16         173         35           Am9102D         1024 x 1         250         C         +5         3-State         Separate         16         290         42           Am9111A         256 x 4         500         C, M         +5         3-State         Bussed         18         290         46           Am9111B         256 x 4         400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Am9101E        | 256 × 4           | 200                               | С              | +5                | 3-State |                                       | 22              | 315                                |                                  |

| Am9102A         1024 x 1         500         C, M         +5         3-State         Separate         16         263         42           Am91L02A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am9102D         1024 x 1         250         C         +5         3-State         Separate         16         290         42           Am9102E         1024 x 1         200         C         +5         3-State         Separate         16         290         42           Am9111A         256 x 4         500         C, M         +5         3-State         Bussed         18         290         46           Am91L1B         256 x 4         400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Am9102         | 1024 x 1          | 650                               | C, M           | +5                | 3-State | Separate                              | 16              | 263                                | 42                               |

| Am91L02A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         263         42           Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         263         42           Am91L02C         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am91L02C         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am9102D         1024 x 1         250         C         +5         3-State         Separate         16         290         42           Am9102E         1024 x 1         200         C         +5         3-State         Separate         16         290         42           Am9111A         256 x 4         500         C, M         +5         3-State         Bussed         18         290         46           Am9111B         256 x 4         400         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Am91L02        | 1024 x 1          | 650                               | C, M           | +5                | 3-State | Separate                              | 16              | 158                                | 35                               |

| Am91L02A         1024 x 1         500         C, M         +5         3-State         Separate         16         158         35           Am9102B         1024 x 1         400         C, M         +5         3-State         Separate         16         263         42           Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am9102D         1024 x 1         250         C         +5         3-State         Separate         16         290         42           Am9102E         1024 x 1         200         C         +5         3-State         Separate         16         290         42           Am9111A         256 x 4         500         C, M         +5         3-State         Bussed         18         290         46           Am9111B         256 x 4         400         C, M         +5         3-State         Bussed         18         173         37           Am9111C         256 x 4         300         C,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Am9102A        | 1024 x 1          | 500                               | C, M           | +5                |         |                                       | 16              | 263                                |                                  |

| Am91L02B 1024 x 1 400 C, M +5 3-State Separate 16 158 35 Am9102C 1024 x 1 300 C, M +5 3-State Separate 16 290 42 Am91L02C 1024 x 1 300 C, M +5 3-State Separate 16 290 42 Am91L02C 1024 x 1 250 C +5 3-State Separate 16 290 42 Am9102E 1024 x 1 250 C +5 3-State Separate 16 290 42 Am9102E 1024 x 1 200 C +5 3-State Separate 16 290 42 Am9111A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11A 256 x 4 400 C, M +5 3-State Bussed 18 173 37 Am9111C 256 x 4 300 C, M +5 3-State Bussed 18 173 37 Am91L1C 256 x 4 300 C, M +5 3-State Bussed 18 189 37 Am9111E 256 x 4 400 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 250 C +5 3-State Bussed 18 315 46 Am91L11A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L12A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L12A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am9112C 256 x 4 300 C, M +5 3-State Bussed 16 173 37 Am9112B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am9112C 256 x 4 300 C, M +5 3-State Bussed 16 173 37 Am9112C 256 x 4 300 C, M +5 3-State Bussed 16 189 37 Am9112C 256 x 4 500 C, M +5 3-State Bussed 16 315 46 Am91L12B 256 x 4 500 C, M +5 3-State Bussed 16 315 46 Am9112D 256 x 4 500 C, M +5 3-State Bussed 16 315 46 Am9112D 256 x 4 500 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 500 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Separate 22 578 84 | Am91 L02A      | 1024 x 1          | 500                               |                | +5                | 3-State | Separate                              | 16              | 158                                |                                  |

| Am91L02B         1024 x 1         400         C, M         +5         3-State         Separate         16         158         35           Am9102C         1024 x 1         300         C, M         +5         3-State         Separate         16         290         42           Am91L02C         1024 x 1         300         C, M         +5         3-State         Separate         16         173         35           Am9102D         1024 x 1         250         C         +5         3-State         Separate         16         290         42           Am9102E         1024 x 1         200         C         +5         3-State         Separate         16         290         42           Am91L11A         256 x 4         500         C, M         +5         3-State         Bussed         18         290         46           Am91L11B         256 x 4         400         C, M         +5         3-State         Bussed         18         173         37           Am91L11C         256 x 4         400         C, M         +5         3-State         Bussed         18         173         37           Am91L1D         256 x 4         250         C<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Am9102B        | 1024 x 1          | 400                               |                | +5                | 3-State | · · · · · · · · · · · · · · · · · · · |                 |                                    |                                  |

| Am91L02C 1024 x 1 300 C, M +5 3-State Separate 16 173 35 Am9102D 1024 x 1 250 C +5 3-State Separate 16 290 42 Am9102E 1024 x 1 200 C +5 3-State Separate 16 290 42 Am9111A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 173 37 Am91L1C 256 x 4 300 C, M +5 3-State Bussed 18 173 37 Am91L1C 256 x 4 300 C, M +5 3-State Bussed 18 189 37 Am91L1C 256 x 4 300 C, M +5 3-State Bussed 18 189 37 Am91L1D 256 x 4 250 C +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am911D 256 x 4 250 C +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140B 4096 x 1 400 C, M +5 3-State Bussed 22 578 84 Am9140B 4096 x 1 400 C, M +5 3-State Separate 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Separate 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Separate 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Separate 22 578 84 Am9140B 4096 x | Am91L02B       | 1024 × 1          | 400                               |                | +5                | 3-State | 100                                   | 16              | 158                                |                                  |

| Am9102D 1024 x 1 250 C +5 3-State Separate 16 290 42 Am9102E 1024 x 1 200 C +5 3-State Separate 16 290 42 Am9111A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 173 37 Am9111C 256 x 4 300 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 300 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 300 C, M +5 3-State Bussed 18 315 46 Am9111D 256 x 4 250 C +5 3-State Bussed 18 315 46 Am9111D 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am9112A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L12A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 290 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 290 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 173 37 Am9112B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 173 37 Am9112D 256 x 4 250 C +5 3-State Bussed 16 173 37 Am9112C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am9112D 256 x 4 250 C +5 3-State Bussed 16 315 46 Am9112D 256 x 4 250 C +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9130C 1024 x 4 200 C +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Separate 22 578 84 Am9140B 4096 x 1 500 C, M +5 3-State Separate 22 578 84                                                                                                                                                                                                                                                                                                | Am9102C        | 1024 x 1          | 300                               |                | +5                | 3-State | Separate                              | 16              | 290                                | 42                               |

| Am9102E 1024 x 1 200 C +5 3-State Separate 16 290 42 Am9111A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 173 37 Am91L11C 256 x 4 300 C, M +5 3-State Bussed 18 173 37 Am9111C 256 x 4 300 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 300 C, M +5 3-State Bussed 18 189 37 Am9111D 256 x 4 250 C +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L2A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L2A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L12B 256 x 4 400 C, M +5 3-State Bussed 16 173 37 Am9112C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L12C 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am9112D 256 x 4 250 C +5 3-State Bussed 16 315 46 Am9112D 256 x 4 250 C +5 3-State Bussed 16 315 46 Am9130A 1024 x 4 500 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 200 C +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 200 C +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84                                                                                                                                                                                                                                                                                                                                                                                                              | Am91L02C       | 1024 x 1          | 300                               | C, M           | +5                | 3-State | Separate                              | 16              | 173                                | 35                               |

| Am9111A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11A 256 x 4 500 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 290 46 Am91L11B 256 x 4 400 C, M +5 3-State Bussed 18 173 37 Am9111C 256 x 4 300 C, M +5 3-State Bussed 18 315 46 Am91L11C 256 x 4 300 C, M +5 3-State Bussed 18 189 37 Am9111D 256 x 4 250 C +5 3-State Bussed 18 315 46 Am91L1E 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 18 315 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L1B 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L1A 256 x 4 500 C, M +5 3-State Bussed 16 290 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 290 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 400 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 300 C, M +5 3-State Bussed 16 315 46 Am91L1B 256 x 4 250 C +5 3-State Bussed 16 315 46 Am911D 256 x 4 250 C +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 400 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 300 C, M +5 3-State Bussed 22 578 84 Am9130B 1024 x 4 200 C +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84 Am9140A 4096 x 1 500 C, M +5 3-State Bussed 22 578 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Am9102D        | 1024 x 1          | 250                               | С              | +5                | 3-State | Separate                              | 16              | 290                                | 42                               |

| Am91L11A       256 x 4       500       C, M       +5       3-State       Bussed       18       173       37         Am9111B       256 x 4       400       C, M       +5       3-State       Bussed       18       290       46         Am91L11B       256 x 4       400       C, M       +5       3-State       Bussed       18       173       37         Am91L1C       256 x 4       300       C, M       +5       3-State       Bussed       18       189       37         Am91L1D       256 x 4       300       C, M       +5       3-State       Bussed       18       115       46         Am91L1D       256 x 4       250       C       +5       3-State       Bussed       18       315       46         Am91L12A       256 x 4       200       C       +5       3-State       Bussed       16       290       46         Am91L12A       256 x 4       500       C, M       +5       3-State       Bussed       16       173       37         Am9112B       256 x 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Am9102E        | 1024 x 1          | 200                               | C              | +5                | 3-State | Separate                              | 16              | 290                                | 42                               |

| Am9111B       256 x 4       400       C, M       +5       3-State       Bussed       18       290       46         Am91L11B       256 x 4       400       C, M       +5       3-State       Bussed       18       173       37         Am9111C       256 x 4       300       C, M       +5       3-State       Bussed       18       315       46         Am9111D       256 x 4       300       C, M       +5       3-State       Bussed       18       315       46         Am9111D       256 x 4       250       C       +5       3-State       Bussed       18       315       46         Am9111E       256 x 4       250       C       +5       3-State       Bussed       18       315       46         Am9112A       256 x 4       200       C       +5       3-State       Bussed       16       290       46         Am9112B       256 x 4       500       C, M       +5       3-State       Bussed       16       173       37         Am9112B       256 x 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C       25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Am9111A        | 256 x 4           | 500                               | C, M           | +5                | 3-State | Bussed                                | 18              | 290                                | 46                               |

| Am91L11B       256 × 4       400       C, M       +5       3-State       Bussed       18       173       37         Am9111C       256 × 4       300       C, M       +5       3-State       Bussed       18       315       46         Am91L11C       256 × 4       300       C, M       +5       3-State       Bussed       18       189       37         Am9111D       256 × 4       250       C       +5       3-State       Bussed       18       315       46         Am9111E       256 × 4       200       C       +5       3-State       Bussed       18       315       46         Am9112A       256 × 4       500       C, M       +5       3-State       Bussed       16       290       46         Am9112B       256 × 4       500       C, M       +5       3-State       Bussed       16       173       37         Am9112B       256 × 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C       256 × 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112D <t< td=""><td>Am91L11A</td><td>256 × 4</td><td>500</td><td>C, M</td><td>+5.</td><td>3-State</td><td>Bussed</td><td>18</td><td>173</td><td>37</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Am91L11A       | 256 × 4           | 500                               | C, M           | +5.               | 3-State | Bussed                                | 18              | 173                                | 37                               |

| Am9111C       256 x 4       300       C, M       +5       3-State       Bussed       18       315       46         Am91L11C       256 x 4       300       C, M       +5       3-State       Bussed       18       189       37         Am9111D       256 x 4       250       C       +5       3-State       Bussed       18       315       46         Am9111E       256 x 4       200       C       +5       3-State       Bussed       18       315       46         Am9112A       256 x 4       500       C, M       +5       3-State       Bussed       16       290       46         Am9112B       256 x 4       500       C, M       +5       3-State       Bussed       16       173       37         Am9112B       256 x 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C       256 x 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C       256 x 4       300       C, M       +5       3-State       Bussed       16       189       37         Am9112D <td< td=""><td>Am9111B</td><td>256 x 4</td><td>400</td><td>C, M</td><td>+5</td><td>3-State</td><td>Bussed</td><td>18</td><td>290</td><td>46</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Am9111B        | 256 x 4           | 400                               | C, M           | +5                | 3-State | Bussed                                | 18              | 290                                | 46                               |

| Am91L11C       256 x 4       300       C, M       +5       3-State       Bussed       18       189       37         Am9111D       256 x 4       250       C       +5       3-State       Bussed       18       315       46         Am9111E       256 x 4       200       C       +5       3-State       Bussed       18       315       46         Am9112A       256 x 4       500       C, M       +5       3-State       Bussed       16       290       46         Am91L12A       256 x 4       500       C, M       +5       3-State       Bussed       16       173       37         Am9112B       256 x 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C       256 x 4       400       C, M       +5       3-State       Bussed       16       173       37         Am9112C       256 x 4       300       C, M       +5       3-State       Bussed       16       189       37         Am9112D       256 x 4       250       C       +5       3-State       Bussed       16       315       46         Am9112E       2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Am91L11B       | 256 x 4           | 400                               | C, M           | +5                | 3-State | Bussed                                | 18              | 173                                | 37                               |